# X20DS1319

# 1 General information

The module being used is a multifunctional digital signal processor module. It's flexibility allows it to be implemented for a wide range of tasks involving the creation or processing of digital signals. For example, two main uses include encoder emulation and controlling stepper output stages with pulse and direction signals. When used for encoder emulation, frequency inverters or servo axes with the speed follow function can follow a real or virtual master axis.

A further important feature is the timestamp function, which is integrated in the module. It can be used, for example, to create ramp curves for the counter in the encoder emulation virtually independent of bus cycle times. It's only necessary to enter the target counter value and the time at which it should be reached. The module generates the appropriate counter values, precisely in microsecond resolution and independently of the bus clock.

- · 4 digital input channels

- · 4 digital channels, configurable as inputs or outputs

- 1 universal counter pair (2 event counters, AB counter or up/down counter)

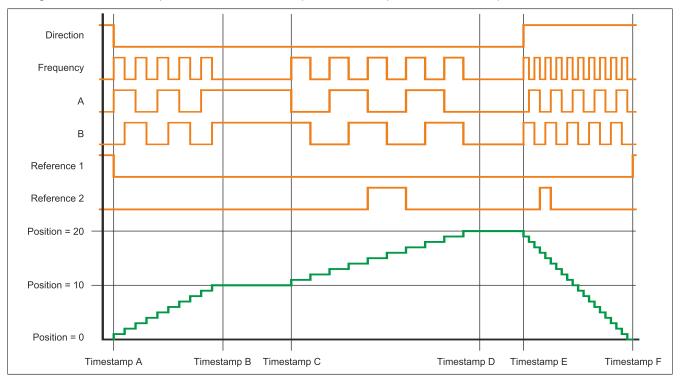

- Linear movement generator (A/B; direction/frequency) with up to 2 reference pulses

- · SSI absolute encoder

# 2 Order data

| Model number | Short description                                                                                                                                                                                                                                                                                                                   | Figure            |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|

|              | Digital signal processing and preparation                                                                                                                                                                                                                                                                                           |                   |  |  |

| X20DS1319    | X20 multifunctional digital signal processor, 4 digital input channels, 4 digital channels configurable as inputs or outputs, 2 event counters, 1 universal counter pair configurable as A/B or up/down counter, linear movement generator (A/B, direction/frequency) with 2 reference pulses, SSI absolute encoder, NetTime module | ent<br>up/<br>re- |  |  |

|              | Required accessories                                                                                                                                                                                                                                                                                                                |                   |  |  |

|              | Bus modules                                                                                                                                                                                                                                                                                                                         |                   |  |  |

| X20BM11      | X20 bus module, 24 VDC keyed, internal I/O supply continuous                                                                                                                                                                                                                                                                        | 4                 |  |  |

| X20BM15      | X20 bus module, with node number switch, 24 VDC keyed, internal I/O supply continuous                                                                                                                                                                                                                                               |                   |  |  |

|              | Terminal blocks                                                                                                                                                                                                                                                                                                                     |                   |  |  |

| X20TB12      | X20 terminal block, 12-pin, 24 VDC keyed                                                                                                                                                                                                                                                                                            |                   |  |  |

Table 1: X20DS1319 - Order data

# 3 Technical data

| Model number                                      | X20DS1319                                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Short description                                 |                                                                                                                                                                                                                                                                                                                                                                          |

| I/O module                                        | 4 digital input channels, 4 digital channels configurable as inputs or outputs, 1 universal counter pair (2 event counters, AB counter or up/down counter), linear movement generator (A/B; direction/frequency) with up to two reference pulses, SSI absolute encoder, relative or absolute times of input edges in μs resolution, time-triggered I/O, I/O oversampling |

| General information                               |                                                                                                                                                                                                                                                                                                                                                                          |

| B&R ID code                                       | 0x2547                                                                                                                                                                                                                                                                                                                                                                   |

| Status indicators                                 | I/O function per channel, operating state, module status                                                                                                                                                                                                                                                                                                                 |

| Diagnostics Modulo run/orrer                      | Voc. using status LED and software                                                                                                                                                                                                                                                                                                                                       |

| Module run/error Outputs                          | Yes, using status LED and software  Yes, using status LED                                                                                                                                                                                                                                                                                                                |

| Power consumption                                 | res, using status LLD                                                                                                                                                                                                                                                                                                                                                    |

| Bus                                               | 0.01 W                                                                                                                                                                                                                                                                                                                                                                   |

| Internal I/O                                      | 1.5 W                                                                                                                                                                                                                                                                                                                                                                    |

| Additional power dissipation caused by the actua- |                                                                                                                                                                                                                                                                                                                                                                          |

| tors (resistive) [W]                              |                                                                                                                                                                                                                                                                                                                                                                          |

| Electrical isolation                              |                                                                                                                                                                                                                                                                                                                                                                          |

| Channel - Bus                                     | Yes                                                                                                                                                                                                                                                                                                                                                                      |

| Channel - Channel                                 | No                                                                                                                                                                                                                                                                                                                                                                       |

| Type of signal lines                              | Shielded cables must be used for all signal lines.                                                                                                                                                                                                                                                                                                                       |

| Certification                                     | V                                                                                                                                                                                                                                                                                                                                                                        |

| CE                                                | Yes                                                                                                                                                                                                                                                                                                                                                                      |

| KC<br>UL                                          | Yes<br>cULus E115267                                                                                                                                                                                                                                                                                                                                                     |

| UL                                                | CULUS E115267 Industrial control equipment                                                                                                                                                                                                                                                                                                                               |

| HazLoc                                            | cCSAus 244665                                                                                                                                                                                                                                                                                                                                                            |

|                                                   | Process control equipment                                                                                                                                                                                                                                                                                                                                                |

|                                                   | for hazardous locations                                                                                                                                                                                                                                                                                                                                                  |

|                                                   | Class I, Division 2, Groups ABCD, T5                                                                                                                                                                                                                                                                                                                                     |

| ATEX                                              | Zone 2, II 3G Ex nA nC IIA T5 Gc<br>IP20, Ta = 0 - Max. 60°C                                                                                                                                                                                                                                                                                                             |

|                                                   | FTZÚ 09 ATEX 0083X                                                                                                                                                                                                                                                                                                                                                       |

| DNV GL                                            | Temperature: <b>B</b> (0 - 55°C)                                                                                                                                                                                                                                                                                                                                         |

|                                                   | Humidity: B (up to 100%)                                                                                                                                                                                                                                                                                                                                                 |

|                                                   | Vibration: <b>B</b> (4 g)                                                                                                                                                                                                                                                                                                                                                |

| - 5                                               | EMC: <b>B</b> (Bridge and open deck)                                                                                                                                                                                                                                                                                                                                     |

| LR<br>GOST-R                                      | ENV1<br>Yes                                                                                                                                                                                                                                                                                                                                                              |

| Linear movement generator                         | 165                                                                                                                                                                                                                                                                                                                                                                      |

| Quantity                                          | 1                                                                                                                                                                                                                                                                                                                                                                        |

| Encoder outputs                                   | 24 V, asymmetrical (A/B; direction/frequency)                                                                                                                                                                                                                                                                                                                            |

| Counter size                                      | 16/32-bit                                                                                                                                                                                                                                                                                                                                                                |

| Digital inputs                                    |                                                                                                                                                                                                                                                                                                                                                                          |

| Quantity                                          | 4 + 4, configurable as inputs or outputs using software                                                                                                                                                                                                                                                                                                                  |

| Nominal voltage                                   | 24 VDC                                                                                                                                                                                                                                                                                                                                                                   |

| Input voltage                                     | 24 VDC -15 % / +20 %                                                                                                                                                                                                                                                                                                                                                     |

| Input current at 24 VDC                           | Approx. 1.3 mA                                                                                                                                                                                                                                                                                                                                                           |

| Input filter                                      |                                                                                                                                                                                                                                                                                                                                                                          |

| Hardware                                          | ≤2 µs                                                                                                                                                                                                                                                                                                                                                                    |

| Software                                          | -<br>Cink                                                                                                                                                                                                                                                                                                                                                                |

| Input circuit                                     | Sink                                                                                                                                                                                                                                                                                                                                                                     |

| Additional functions                              | SSI absolute encoder, universal counter pair, latch function for universal counter pair                                                                                                                                                                                                                                                                                  |

| Input resistance Input frequency                  | 18.4 kΩ<br>100 kHz                                                                                                                                                                                                                                                                                                                                                       |

| Switching threshold                               | IVU NTZ                                                                                                                                                                                                                                                                                                                                                                  |

| Low                                               | <5 VDC                                                                                                                                                                                                                                                                                                                                                                   |

| High                                              | >15 VDC                                                                                                                                                                                                                                                                                                                                                                  |

| Overload characteristics of encoder power supply  | Short circuit protection, overload protection                                                                                                                                                                                                                                                                                                                            |

| Isolation voltage between channel and bus         | 500 V <sub>eff</sub>                                                                                                                                                                                                                                                                                                                                                     |

| SSI absolute encoder                              |                                                                                                                                                                                                                                                                                                                                                                          |

| Quantity                                          | 1                                                                                                                                                                                                                                                                                                                                                                        |

| Counter size                                      | Encoder-dependent up to 32-bit                                                                                                                                                                                                                                                                                                                                           |

| Max. transfer rate                                | 125 kbit/s                                                                                                                                                                                                                                                                                                                                                               |

| Encoder power supply                              | Module-internal, max. 600 mA                                                                                                                                                                                                                                                                                                                                             |

| Nominal voltage                                   | 24 V, asymmetrical                                                                                                                                                                                                                                                                                                                                                       |

| Universal counter pair                            |                                                                                                                                                                                                                                                                                                                                                                          |

| Quantity                                          | 1                                                                                                                                                                                                                                                                                                                                                                        |

| Operating modes                                   | 2x event counter, up/down counter, AB counter                                                                                                                                                                                                                                                                                                                            |

| Encoder inputs                                    | 24 V, asymmetrical                                                                                                                                                                                                                                                                                                                                                       |

| Counter size                                      | 16/32-bit                                                                                                                                                                                                                                                                                                                                                                |

| Input frequency                                   | Max. 100 kHz                                                                                                                                                                                                                                                                                                                                                             |

Table 2: X20DS1319 - Technical data

| Model number                                        | X20DS1319                                                                                              |  |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------|--|

| Evaluation                                          |                                                                                                        |  |

| AB counter                                          | 4x                                                                                                     |  |

| Event counter                                       | 2x                                                                                                     |  |

| Up/Down counter                                     | 2x                                                                                                     |  |

| Signal form                                         | Square wave pulse                                                                                      |  |

| Encoder power supply                                | Module-internal, max. 600 mA                                                                           |  |

| Digital outputs                                     |                                                                                                        |  |

| Design                                              | Push / Pull / Push-Pull                                                                                |  |

| Quantity                                            | Up to 4, configurable as inputs or outputs using software                                              |  |

| Nominal voltage                                     | 24 VDC                                                                                                 |  |

| Switching voltage                                   | 24 VDC -15 % / +20 %                                                                                   |  |

| Nominal output current                              | 0.1 A                                                                                                  |  |

| Total nominal current                               | 0.4 A                                                                                                  |  |

| Output circuit                                      | Sink and/or source                                                                                     |  |

| Output protection                                   | Thermal cutoff if overcurrent or short circuit occurs, integrated protection for switching inductances |  |

| Diagnostic status                                   | Output monitoring                                                                                      |  |

| Leakage current when switched off                   | Max. 25 µA                                                                                             |  |

| Residual voltage                                    | <0.9 V at 0.1 A rated current                                                                          |  |

| Peak short circuit current                          | <10 A                                                                                                  |  |

| Switching on after overload or short circuit cutoff | Approx. 10 ms (depends on the module temperature)                                                      |  |

| Switching delay                                     | , pp                                                                                                   |  |

| 0 -> 1                                              | <2 µs                                                                                                  |  |

| 1 -> 0                                              | <2 μs                                                                                                  |  |

| Switching frequency                                 | <del>-</del> F*                                                                                        |  |

| Resistive load                                      | Max. 125 kHz                                                                                           |  |

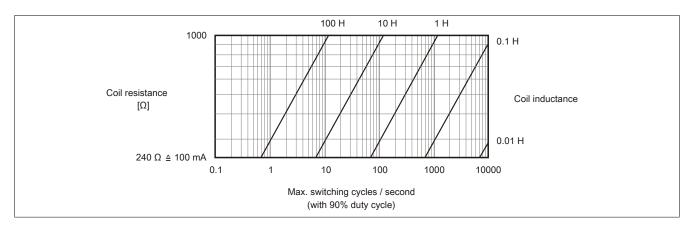

| Inductive load                                      | See section "Switching inductive loads"                                                                |  |

| Braking voltage when switching off inductive loads  | Switching voltage + 0.6 VDC                                                                            |  |

| Additional functions                                | Timing for SSI absolute encoder, linear movement generator                                             |  |

| Operating conditions                                | <b>3</b> • • • • • • • • • • • • • • • • • • •                                                         |  |

| Mounting orientation                                |                                                                                                        |  |

| Horizontal                                          | Yes                                                                                                    |  |

| Vertical                                            | Yes                                                                                                    |  |

| Installation at elevations above sea level          | ·                                                                                                      |  |

| 0 to 2000 m                                         | No limitations                                                                                         |  |

| >2000 m                                             | Reduction of ambient temperature by 0.5°C per 100 m                                                    |  |

| EN 60529 protection                                 | IP20                                                                                                   |  |

| Environmental conditions                            |                                                                                                        |  |

| Temperature                                         |                                                                                                        |  |

| Operation                                           |                                                                                                        |  |

| Horizontal installation                             | -25 to 60°C                                                                                            |  |

| Vertical installation                               | -25 to 50°C                                                                                            |  |

| Derating                                            | -                                                                                                      |  |

| Storage                                             | -40 to 85°C                                                                                            |  |

| Transport                                           | -40 to 85°C                                                                                            |  |

| Relative humidity                                   |                                                                                                        |  |

| Operation                                           | 5 to 95%, non-condensing                                                                               |  |

| Storage                                             | 5 to 95%, non-condensing                                                                               |  |

| Transport                                           | 5 to 95%, non-condensing                                                                               |  |

| Mechanical characteristics                          |                                                                                                        |  |

| Note                                                | Order 1x X20TB12 terminal block separately<br>Order 1x X20BM11 bus module separately                   |  |

| Spacing                                             | 12.5 <sup>+0.2</sup> mm                                                                                |  |

|                                                     |                                                                                                        |  |

Table 2: X20DS1319 - Technical data

# 4 LED status indicators

For a description of the various operating modes, see section "Additional information - Diagnostic LEDs" of the X20 system user's manual.

| Figure  | LED                                     | Color | Status       | Description                                      |

|---------|-----------------------------------------|-------|--------------|--------------------------------------------------|

|         | r                                       | Green | Off          | No power to module                               |

|         |                                         |       | Single flash | RESET mode                                       |

|         | Double flash BOOT mode (during firmware |       | Double flash | BOOT mode (during firmware update) <sup>1)</sup> |

|         |                                         |       | Blinking     | PREOPERATIONAL mode                              |

|         |                                         |       | On           | RUN mode                                         |

| 0 9     | е                                       | Red   | Off          | No power to module or everything OK              |

| E 1 2 5 |                                         |       | Single flash | I/O error. Possible causes:                      |

| S 5 6   |                                         |       |              | SSI error <sup>2)</sup>                          |

| SQ 023  |                                         |       | Double flash | System error. Possible causes:                   |

| Ž       |                                         |       |              | Motion function error <sup>3)</sup>              |

|         |                                         |       |              | I/O oversampling error <sup>4)</sup>             |

|         |                                         |       |              | Edge detection error <sup>4)</sup>               |

|         |                                         |       | Triple flash | I/O error and system error occur together        |

|         |                                         |       | On           | Error or reset status                            |

|         | 1 - 8                                   | Green |              | Status of the corresponding digital signal       |

- 1) Depending on the configuration, a firmware update can take up to several minutes.

- 2) See "Error state SSI" on page 13 register for the exact error description.

- 3) See "Error state Motion functions" on page 13 register for the exact error description.

- 4) See "Error state Output data and edge detection" on page 12 register for the exact error description.

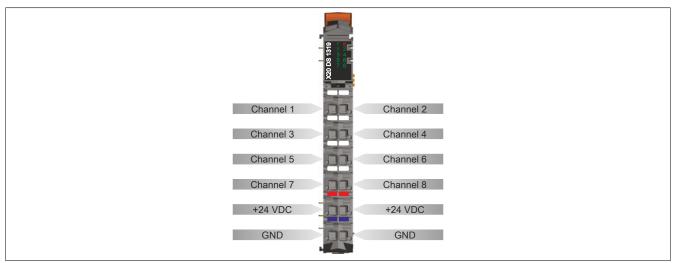

# **5 Pinout**

Shielded cables must be used for all signal lines.

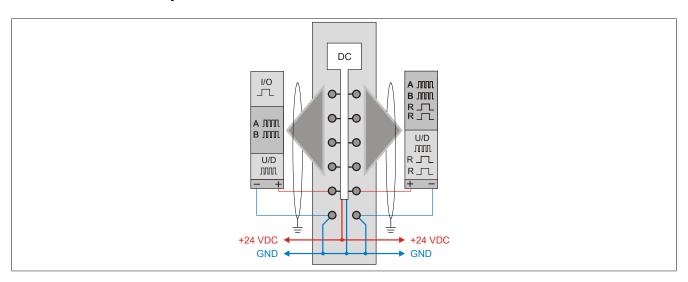

# 6 Connection example

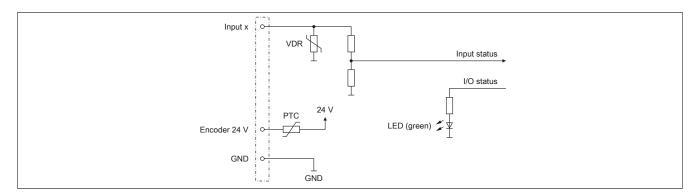

# 7 Input circuit diagram

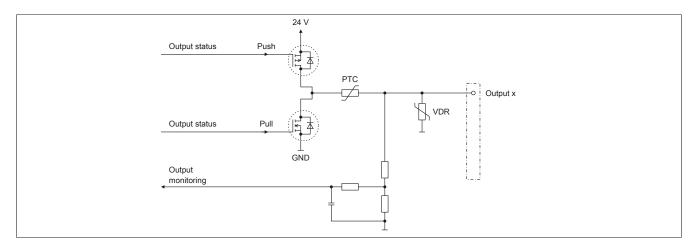

# 8 Output circuit diagram

# 9 Switching inductive loads

# **10 Connection options**

# Digital input/output

| Channel | Function       |

|---------|----------------|

| 1       | Input          |

| 2       | Input          |

| 3       | Input / Output |

| 4       | Input / Output |

| 5       | Input          |

| 6       | Input          |

| 7       | Input / Output |

| 8       | Input / Output |

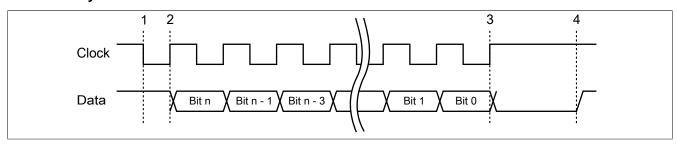

# Wiring of the SSI absolute encoder

| Channel    | Function |

|------------|----------|

| 5 (input)  | Data     |

| 7 (output) | Clock    |

# Wiring of the linear movement generator

| Channel    | Up-Down     | АВ |  |

|------------|-------------|----|--|

| 3 (output) | Direction   | Α  |  |

| 4 (output) | Frequency   | В  |  |

| 7 (output) | Reference 1 |    |  |

| 8 (output) | Reference 2 |    |  |

# Wiring of the universal counter pair

| Channel   | Edge counters     | Up/Down counter | Incremental |

|-----------|-------------------|-----------------|-------------|

| 1 (input) | Input 1           | Direction       | Α           |

| 2 (input) | Input 2           | Frequency       | В           |

| 5 (input) | Latch input 1 (R) |                 |             |

| 6 (input) | Latch input 2 (E) |                 |             |

# 11 Register description

# 11.1 General data points

In addition to the registers listed in the register description, the module also has other more general data points. These registers are not specific to the module but contain general information such as serial number and hardware version.

These general data points are listed in section "Additional information - General data points" of the X20 system user's manual.

# 11.2 Function model 0 - default

| Register             | Name                                                                    | Data type | Read     |         | Write  |          |

|----------------------|-------------------------------------------------------------------------|-----------|----------|---------|--------|----------|

|                      |                                                                         |           | Cyclic   | Acyclic | Cyclic | Acyclic  |

| Configuration        | ,                                                                       |           |          |         |        |          |

| 513                  | CfO_SlframeGenID                                                        | USINT     |          |         |        | •        |

|                      | - System timer                                                          |           |          |         |        |          |

| 642                  | CfO_SystemCycleTime                                                     | UINT      |          |         |        | •        |

| 646                  | CfO_SystemCycleOffset                                                   | INT       |          |         |        | •        |

| 650                  | CfO_SystemCyclePrescaler                                                | UINT      |          |         |        | •        |

|                      | - Physical I/O                                                          |           |          |         |        |          |

| 769 +<br>(N-1) * 2   | CfO_PhyIOConfigCh0N (Index N = 1 to 8)                                  | USINT     |          |         |        | •        |

| onfiguration         | - Direct I/O                                                            |           |          |         |        |          |

| 899                  | CfO DirectIOClearMask0 7                                                | USINT     |          |         |        | •        |

| 903                  | CfO DirectIOSetMask0 7                                                  | USINT     |          |         |        | •        |

| 905                  | CfO OutputUpdateCycle                                                   | USINT     |          |         |        | •        |

|                      | - Oversampled I/O                                                       |           |          |         |        |          |

| 1025                 | CfO OversampleMode                                                      | USINT     |          |         |        | •        |

| 1027                 | CfO_OversampleSampleCycleID                                             | USINT     |          |         |        | •        |

| 1029                 | CfO OversampleRelativeCycleID                                           | USINT     |          |         |        | •        |

| 1023                 | CfO OversampleConsumeCycleID                                            | USINT     |          |         |        | •        |

| 1033                 | CfO OversampleOutputBits                                                | USINT     |          |         |        | •        |

| 1035                 | CfO OversampleInputBits                                                 | USINT     |          |         |        | •        |

| 1033                 | CfO OversampleOutputWindow                                              | USINT     |          |         |        | •        |

| 1037                 | _ : :                                                                   | USINT     |          |         |        |          |

| 1039<br>1041 + (N*2) | CfO_OversampleInputWindow CfO_OversampleConfigInputN (Index N = 0 to 3) | USINT     |          |         |        | •        |

|                      |                                                                         |           |          |         |        | •        |

| 1049 + (N*2)         | CfO_OversampleConfigOutputN (Index N = 0 to 3)                          | USINT     |          |         |        | •        |

|                      | - Edge detection                                                        | LIOINIT   |          |         |        |          |

| 1537                 | CfO_EdgeDetectPollCycleID                                               | USINT     |          |         |        | •        |

| 1548                 | CfO_EdgeDetectEventEnable                                               | UDINT     |          |         |        | •        |

| 1665 +<br>(N-1) * 16 | CfO_EdgeDetectUnit0NMode (Index N = 1 to 4)                             | USINT     |          |         |        | •        |

| 1667 +<br>(N-1) * 16 | CfO_EdgeDetectUnit0NLeading (Index N = 1 to 4)                          | USINT     |          |         |        | •        |

| 1669 +<br>(N-1) * 16 | CfO_EdgeDetectUnit0NMaster (Index N = 1 to 4)                           | USINT     |          |         |        | •        |

| 1671 +<br>(N-1) * 16 | CfO_EdgeDetectUnit0NSlave (Index N = 1 to 4)                            | USINT     |          |         |        | •        |

| Configuration        | - Movement functions                                                    |           | <u> </u> |         |        | <u>'</u> |

| 4097                 | CfO FifoSize                                                            | USINT     |          |         |        | •        |

| 4099                 | CfO Mode                                                                | SINT      |          |         |        | •        |

| 4101                 | CfO SpeedLimit                                                          | USINT     |          |         |        | •        |

| 4103                 | CfO FormatAdjust                                                        | USINT     |          |         |        | •        |

| 4105                 | CfO TimeStampRange                                                      | SINT      |          |         |        | •        |

| 4107                 | CfO PositionRange                                                       | SINT      |          |         |        | •        |

| 4109                 | CfO Reference0Range                                                     | SINT      |          |         |        | •        |

| 4111                 | CfO Reference1Range                                                     | SINT      |          |         |        |          |

| 4116                 | CfO_TimeStampDelay                                                      | DINT      |          |         |        | •        |

| 4124                 | CfO SpeedCycleTime 32bit                                                | UDINT     |          |         |        | •        |

|                      | CfO_SpeedCycle i Ime_32bit CfO ResolPosition                            |           |          |         |        |          |

| 4129                 |                                                                         | SINT      |          |         |        | •        |

| 4131                 | CfO_ResolSpeed                                                          | SINT      |          |         |        | •        |

| 4220                 | CfO_AccelDataInit                                                       | UDINT     |          |         |        | •        |

| 4260                 | CfO_Reference0Start                                                     | DINT      |          |         |        | •        |

| 4268                 | CfO_Reference0StopMargin                                                | DINT      |          |         |        | •        |

| 4276                 | CfO_Reference1Start                                                     | DINT      |          |         |        | •        |

| 4284                 | CfO_Reference1StopMargin                                                | DINT      |          |         |        | •        |

| Configuration        |                                                                         |           |          |         |        |          |

| 2049                 | CfO_CycleSelect                                                         | USINT     |          |         |        | •        |

| 2051                 | CfO_PhysicalMode                                                        | USINT     |          |         |        | •        |

| 2053                 | CfO_DataBits                                                            | USINT     |          |         |        | •        |

| 2055                 | CfO_NullBits                                                            | USINT     |          |         |        | •        |

| <del> </del>         | - Universal counter                                                     |           |          |         |        |          |

| Danistan    | Name                                                        | Data toma | D-     | Read Write |        |          |

|-------------|-------------------------------------------------------------|-----------|--------|------------|--------|----------|

| Register    |                                                             | Data type |        |            |        | 1        |

| 6145        | CfO CountarCycloSalaat                                      | USINT     | Cyclic | Acyclic    | Cyclic | Acyclic  |

| -           | CfO_CounterCycleSelect                                      |           |        |            |        | •        |

| 6147        | CfO_CounterMode                                             | USINT     |        |            |        | •        |

| 6149        | CfO_LatchMode                                               | USINT     |        |            |        | •        |

| 6151        | CfO_LatchComparator                                         | USINT     |        |            |        | •        |

| 6153        | CounterControl                                              | USINT     |        |            | •      |          |

| ·           | CounterReset                                                | Bit 0     |        |            |        |          |

|             | LatchEnable                                                 | Bit 1     |        |            |        |          |

| Communicat  |                                                             |           | ı      | 1          |        |          |

| 546         | ProtocolError (16-bit)                                      | USINT     | •      |            |        |          |

| 547         | ProtocolError (8-bit)                                       | UINT      | •      |            |        |          |

| 550         | ProtocolSequenceViolation (16-bit)                          | UINT      | •      |            |        |          |

| 551         | ProtocolSequenceViolation (8-bit)                           | USINT     | •      |            |        |          |

|             | on - Error register                                         |           |        |            |        |          |

| 257         | Error state - Output data and edge detection                | USINT     | •      |            |        |          |

|             | OutputControlError                                          | Bit 4     |        |            |        |          |

|             | OutputCopyError                                             | Bit 5     |        |            |        |          |

|             | EdgeDetectError                                             | Bit 6     |        |            |        |          |

| 259         | Error state - SSI                                           | USINT     | •      |            |        |          |

|             | SSICycleTimeViolation                                       | Bit 0     |        |            |        |          |

|             | SSIParityError                                              | Bit 1     |        |            |        |          |

| 261         | Error state - Movement functions                            | USINT     | •      |            |        |          |

|             | MovFifoEmpty                                                | Bit 0     |        |            |        |          |

|             | MovFifoFull                                                 | Bit 1     |        |            |        |          |

|             | MovTargetTimeViolation                                      | Bit 2     | ]      |            |        |          |

|             | MovMaxFrequencyViolation                                    | Bit 3     | 1      |            |        |          |

| 321         | Acknowledge error messages - Output data and edge detection | USINT     |        |            | •      |          |

|             | QuitOutputControlError                                      | Bit 4     | 1      |            |        |          |

|             | QuitOutputCopyError                                         | Bit 5     |        |            |        |          |

|             | QuitEdgeDetectError                                         | Bit 6     | 1      |            |        |          |

| 323         | Acknowledge error messages - SSI                            | USINT     |        |            | •      |          |

| 020         | SSIQuitCycleTimeViolation                                   | Bit 0     |        |            | _      |          |

|             | SSIQuitParityError                                          | Bit 1     |        |            |        |          |

| 325         | Acknowledge error messages - Movement functions             | USINT     |        |            | •      |          |

| 020         | MovQuitFifoEmpty                                            | Bit 0     |        |            |        |          |

|             | MovQuitFifoFull                                             | Bit 1     |        |            |        |          |

|             | MovQuitTargetTimeViolation                                  | Bit 2     |        |            |        |          |

|             | MovQuitNaxFrequencyViolation                                | Bit 2     |        |            |        |          |

| Communicati | ion - System timer                                          | DIL 3     |        |            |        |          |

| 683         | SDCLifeCount                                                | SINT      | •      |            |        |          |

|             | ion - Direct I/O                                            | SINT      |        |            |        |          |

| 915         |                                                             | USINT     |        |            | •      |          |

| 915         | "DigitalOutput" register                                    | Bit 2     |        |            | •      |          |

|             | DigitalOutput03                                             |           |        |            |        |          |

|             | DigitalOutput04                                             | Bit 3     |        |            |        |          |

|             | DigitalOutput07                                             | Bit 6     |        |            |        |          |

|             | DigitalOutput08                                             | Bit 7     |        |            |        |          |

| 927         | "DigitalInput" register                                     | USINT     | •      |            |        |          |

|             | DigitalInput01                                              | Bit 0     |        |            |        |          |

|             |                                                             |           |        |            |        |          |

|             | DigitalInput08                                              | Bit 7     |        |            |        |          |

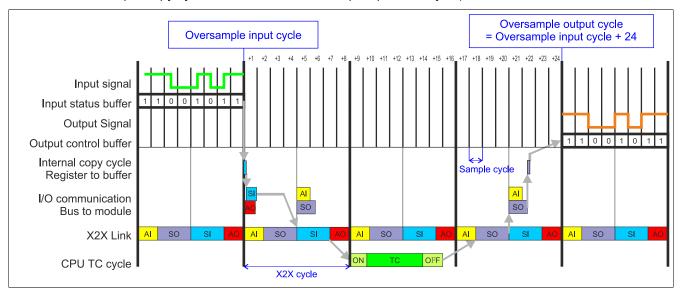

|             | ion - Oversampled I/O (output)                              |           |        |            |        |          |

| 1059        | Oversampling configuration                                  | USINT     |        |            | •      |          |

|             | OversampleEnable                                            | Bit 0     |        |            |        |          |

|             | OversampleOutputValidate                                    | Bit 1     |        |            |        | 1        |

| 1063        | OversampleOutputCycle                                       | USINT     |        |            | •      |          |

|             | OversampleSampleOffset                                      | USINT     |        |            | •      |          |

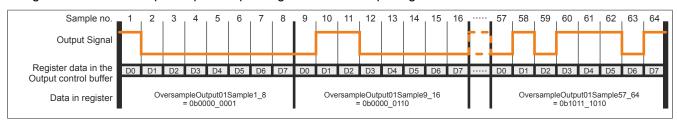

| 1088 + N    | OversampleOutput0NSample1_8 (Index N = 1 to 4)              | USINT     |        |            | •      |          |

| 1092 + N    | OversampleOutput0NSample9_16 (Index N = 1 to 4)             | USINT     |        |            | •      |          |

| 1096 + N    | OversampleOutput0NSample17_24 (Index N = 1 to 4)            | USINT     |        |            | •      |          |

| 1100 + N    | OversampleOutput0NSample25_32 (Index N = 1 to 4)            | USINT     |        |            | •      |          |

| 1104 + N    | OversampleOutput0NSample33_40 (Index N = 1 to 4)            | USINT     |        |            | •      |          |

| 1108 + N    | OversampleOutput0NSample41_48 (Index N = 1 to 4)            | USINT     |        |            | •      |          |

| 1112 + N    | OversampleOutput0NSample49_56 (Index N = 1 to 4)            | USINT     |        |            | •      |          |

| 1116 + N    | OversampleOutput0NSample57_64 (Index N = 1 to 4)            | USINT     |        |            | •      |          |

|             | ion - Oversampled I/O (input)                               |           |        |            |        |          |

| 1074        | OversampleInputTime                                         | INT       | •      |            |        |          |

| 1079        | OversampleInputCycle                                        | USINT     | •      |            |        |          |

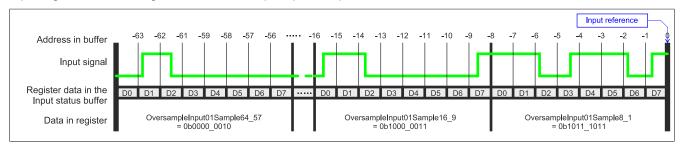

| 1120 + N    | OversampleInput0NSample64 57 (Index N = 1 to 4)             | USINT     | •      |            |        |          |

| 1124 + N    | OversampleInput0NSample56 49 (Index N = 1 to 4)             | USINT     | •      |            |        | <u> </u> |

| 1124 + N    | OversampleInput0NSample48 41 (Index N = 1 to 4)             | USINT     | •      |            |        |          |

| 1132 + N    | OversampleInput0NSample40 33 (Index N = 1 to 4)             | USINT     | •      |            |        | +        |

| 1132 + N    | OversampleInput0NSample32_25 (Index N = 1 to 4)             | USINT     | •      |            |        | +        |

| 1140 + N    | OversampleInput0NSample24_17 (Index N = 1 to 4)             | USINT     | •      |            |        | +        |

| 1140 + N    | OversampleInput0NSample16 9 (Index N = 1 to 4)              | USINT     |        |            |        | +        |

| 1144 T IV   | Oversamplemputorysample ro_s (muex N = 1 to 4)              | USIINI    | •      |            |        |          |

| Dominton             | Name                                                               | Data tura     | Data type Read |               |        | Write   |  |

|----------------------|--------------------------------------------------------------------|---------------|----------------|---------------|--------|---------|--|

| Register             |                                                                    | Data type     | Cyclic         | ad<br>Acyclic | Cyclic | Acyclic |  |

| 1148 + N             | OversampleInput0NSample8_1 (Index N = 1 to 4)                      | USINT         | • Oyelle       | Acyclic       | Cyclic | Acyclic |  |

| _                    | on - Edge detection                                                |               |                |               |        |         |  |

| 1794 +               | EdgeDetect0NMastercount (16-bit) (Index N = 1 to 4)                | INT           | •              |               |        |         |  |

| (N-1) * 32           |                                                                    |               |                |               |        |         |  |

| 1795 +<br>(N-1) * 32 | EdgeDetect0NMastercount (8-bit) (Index N = 1 to 4)                 | SINT          | •              |               |        |         |  |

| 1798 +               | EdgeDetect0NSlavecount (16-bit) (Index N = 1 to 4)                 | INT           | •              |               |        |         |  |

| (N-1) * 32           |                                                                    |               |                |               |        |         |  |

| 1799 +               | EdgeDetect0NSlavecount (8-bit) (Index N = 1 to 4)                  | SINT          | •              |               |        |         |  |

| (N-1) * 32<br>1804 + | EdgeDetect0NDifference (32-bit) (Index N = 1 to 4)                 | DINT          | •              |               |        |         |  |

| (N-1) * 32           | Lage Detection VB merenice (02 bit) (mack 14 - 1 to 4)             | Biiti         |                |               |        |         |  |

| 1806 +               | EdgeDetect0NDifference (16-bit) (Index N = 1 to 4)                 | INT           | •              |               |        |         |  |

| (N-1) * 32           | Educ Duto (ONINA otto Conc. (OO 1/1) (India No. 4 (o. 4)           | DINT          |                |               |        |         |  |

| 1812 +<br>(N-1) * 32 | EdgeDetect0NMastertime (32-bit) (Index N = 1 to 4)                 | DINT          | •              |               |        |         |  |

| 1814 +               | EdgeDetect0NMastertime (16-bit) (Index N = 1 to 4)                 | INT           | •              |               |        |         |  |

| (N-1) * 32           |                                                                    |               |                |               |        |         |  |

| 1820 +<br>(N-1) * 32 | EdgeDetect0NSlavetime (32-bit) (Index N = 1 to 4)                  | DINT          | •              |               |        |         |  |

| 1822 +               | EdgeDetect0NSlavetime (16-bit) (Index N = 1 to 4)                  | INT           | •              |               |        |         |  |

| (N-1) * 32           | .5                                                                 |               |                |               |        |         |  |

|                      | on - Movement functions                                            |               |                |               |        |         |  |

| 4225                 | MovementControl                                                    | USINT         |                |               | •      |         |  |

|                      | MovPosEnable MovSpeedEnable                                        | Bit 0         |                |               |        |         |  |

| 4244                 | MovSpeedEnable  MovTargetTime (32-bit)                             | Bit 1<br>DINT |                |               | •      |         |  |

| 4244                 | MovTargetTime (32-bit) MovTargetTime (16-bit)                      | INT           |                |               | •      |         |  |

| 4252                 | MovTargetPosition (32-bit)                                         | DINT          |                |               | •      |         |  |

| 4254                 | MovTargetPosition (16-bit)                                         | INT           |                |               | •      |         |  |

| 4260                 | MovReference1Start (32-bit)                                        | DINT          |                |               | •      |         |  |

| 4262                 | MovReference1Start (16-bit)                                        | INT           |                |               | •      |         |  |

| 4268<br>4270         | MovReference1StopMargin (32-bit)  MovReference1StopMargin (16-bit) | DINT          |                |               | •      |         |  |

| 4276                 | MovReference2Start (32-bit)                                        | DINT          |                |               | •      |         |  |

| 4278                 | MovReference2Start (16-bit)                                        | INT           |                |               | •      |         |  |

| 4284                 | MovReference2StopMargin (32-bit)                                   | DINT          |                |               | •      |         |  |

| 4286                 | MovReference2StopMargin (16-bit)                                   | INT           |                |               | •      |         |  |

| 4212                 | MovSpeed (32-bit)                                                  | DINT          |                |               | •      |         |  |

| 4210                 | MovSpeed (16-bit)                                                  | INT           |                |               | •      |         |  |

| 4220<br>4218         | MovAcceleration (32-bit) MovAcceleration (16-bit)                  | UDINT         |                |               | •      |         |  |

| 4292                 | MovTimeValid (32-bit)                                              | DINT          | •              |               |        |         |  |

| 4294                 | MovTimeValid (16-bit)                                              | INT           | •              |               |        |         |  |

| 4300                 | MovPosition (32-bit)                                               | DINT          | •              |               |        |         |  |

| 4302                 | MovPosition (16-bit)                                               | INT           | •              |               |        |         |  |

| Communication        |                                                                    | DINT          |                |               | I      |         |  |

| 2084<br>2086         | SSITimeValid (32-bit) SSITimeValid (16-bit)                        | DINT          | •              |               |        |         |  |

| 2000                 | SSITimeChanged (32-bit)                                            | DINT          | •              |               |        |         |  |

| 2094                 | SSITimeChanged (16-bit)                                            | INT           | •              |               |        |         |  |

| 2100                 | SSIPosition (32-bit)                                               | (U)DINT       | •              |               |        |         |  |

| 2102                 | SSIPosition (16-bit)                                               | UINT          | •              |               |        |         |  |

| Communication 6303   | on - Universal counter  LatchCount                                 | CINIT         | _              |               |        |         |  |

| 6308                 | CounterTimeValid (32-bit)                                          | SINT          | •              |               |        |         |  |

| 6310                 | CounterTimeValid (16-bit)                                          | INT           | •              |               |        |         |  |

| 6324                 | Counter01TimeChanged (32-bit)                                      | DINT          | •              |               |        |         |  |

| 6326                 | Counter01TimeChanged (16-bit)                                      | INT           | •              |               |        |         |  |

| 6332                 | Counter02TimeChanged (32-bit)                                      | DINT          | •              |               |        |         |  |

| 6334<br>6340         | Counter02TimeChanged (16-bit) CounterValue01 (32-bit)              | INT<br>DINT   | •              |               |        |         |  |

| 6340                 | CounterValue01 (32-bit) CounterValue01 (16-bit)                    | INT           | •              |               |        |         |  |

| 6348                 | CounterValue02 (32-bit)                                            | DINT          | •              |               |        |         |  |

| 6350                 | CounterValue02 (16-bit)                                            | INT           | •              |               |        |         |  |

| 6356                 | CounterLatch01 (32-bit)                                            | DINT          | •              |               |        |         |  |

| 6358                 | CounterLatch01 (16-bit)                                            | INT           | •              |               |        |         |  |

| 6364                 | CounterLatch02 (32-bit)                                            | DINT          | •              |               |        |         |  |

| 6366<br>6372         | CounterLatch02 (16-bit) CounterRel01 (32-bit)                      | DINT          | •              |               |        |         |  |

| 6374                 | CounterRel01 (32-bit) CounterRel01 (16-bit)                        | INT           | •              |               |        |         |  |

| 6380                 | CounterRel02 (32-bit)                                              | DINT          | •              |               |        |         |  |

| 6382                 | CounterRel02 (16-bit)                                              | INT           | •              |               |        |         |  |

#### 11.3 General

#### 11.3.1 Use with Automation Studio

The module is supported via X2X Link and POWERLINK.

X2X Link supports a up to 28 bytes of synchronous data per module. To optimize use and to prevent needless data transfer, the data points can be adjusted as needed in Automation Studio. Data points that are not needed can be disabled, and the bit width of the data points can be defined.

### 11.3.2 Timestamp function

The timestamp function is based on synchronized timers. When a timestamp event occurs, the module immediately saves the current net time. After the respective data is transmitted to the CPU, including this precise time, the CPU can then evaluate the data using its own net time (or system time).

Conversely, the CPU can predefine output events, apply a timestamp and transfer them to the module. The module then executes the predefined action at the precise time defined by the CPU.

The resolution of the timestamp is up to 1/8 µs in both directions.

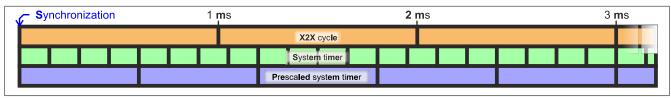

## 11.3.3 Synchronization jitter

Because the CPU – which determines the X2X net time – and the module have different clocks, the module's internal X2X net time must be synchronized with the CPU's net time. Due to this synchronization, the module's internal X2X net time is corrected by a maximum of  $1/8 \mu s$  per system cycle if necessary. This synchronization jitter becomes noticeable when using the net time with  $1/8 \mu s$  resolution (max.  $\pm 1/8 \mu s$ ).

If a 100% exact 1/8 μs resolution without jitter is required, then the "localtime 1/8 μs" must be used (see the "CfO EdgeDetectUnitMode" on page 27 register).

### 11.4 General registers

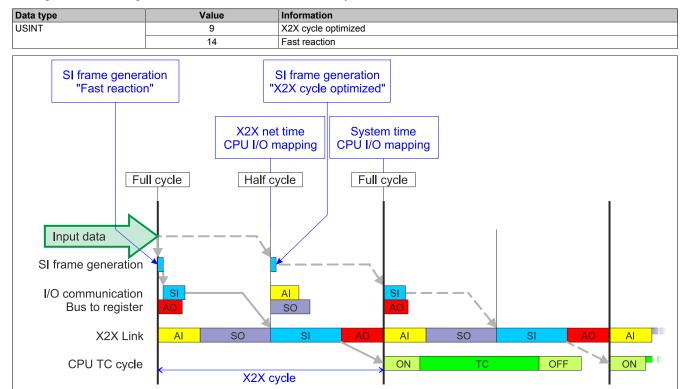

### 11.4.1 Defining the moment for generating synchronous input data

Name:

CfO SlframeGenID

"SI-frame generation" in the Automation Studio I/O configuration.